Indice

ChippaLippa

Il progetto ChippaLippa nasce nella primavera 2018 in seguito all'evento “8bit de noattri” organizzato dall'associazione Firenze Vintage Bit, dove è stato illustrato come realizzare con i componenti discreti della famiglia logica TTL un piccolo processore. Il nostro progetto vanta minor complessità e prevede la realizzazione di un micrcocomputer basato su un derivato del processore MOS 6502 (della stessa famiglia di ben più noti home computer anni '80).

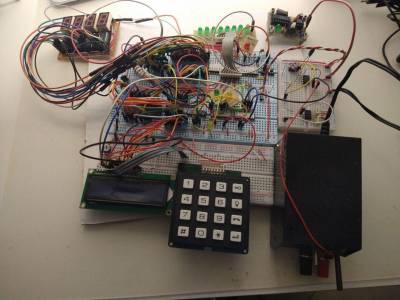

Il ChippaLippa allo step3, attualmente l'ultima versione funzionante:

Materiali acquistati ed a disposizione

- WDC 65C02S (versione statica del MOS 6502)

- Rockwell 6551 (ACIA - Asynchronous Communications Interface Adapter)

- Rockwell 6522 (VIA - Versatile Interface Adapter)

- 74HC00 (porta NAND2 quad)

- 74HC04 (porta NOT hex)

- 74HC139 (2-to-4 decoder/demux)

- SRAM 8Kx8 [di recupero, da testare] IS61C64AH (1pz) e CL63C256N (4pz)

- NE555 q.b.

- HEF4551 (binary to sevseg) (6pz)

Schede realizzate

- Über Retro Programmer: programmatore di EEPROM;

- Clocchino: clock automatico/manuale a duty cycle 50%;

- Stuzzica clock: estensione al clocchino per generare impulsi opportuni (si vedano le note sul clock);

- Bus inspector: semplice display a 7 segmenti per vedere cosa succede sul bus.

Note sul clock

I chip non statici (o farlocchi) permettono di mantenere il livello alto sul segnale di clock per un tempo indefinito. Per operare correttamente, il livello basso deve essere più breve di 5μs.

Fare riferimento allo “Stuzzica clock” ripreso dal circuito debouncer del “6502 primer”.

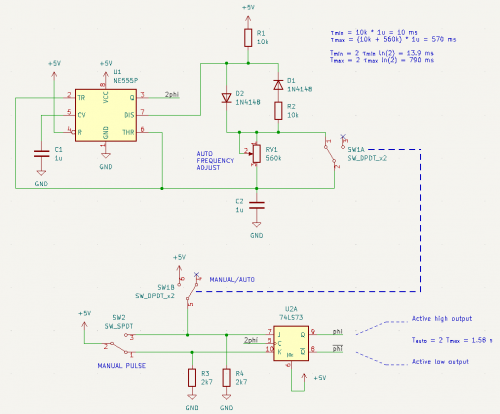

Clocchino

Dovrebbe fare pressappoco quel che fa il clock di Ben Eater, ma con meno chip.

Si tratta di un clock a duplice modalità: automatico (astabile) con frequenza regolabile (0.6-36Hz) e duty cycle fissato a 50%; manuale (monostabile) controllabile tramite la pressione di un bottone e con larghezza di impulso minima garantita di 13ms. Le due modalità possono essere commutate “a caldo” senza la necessità di togliere l'alimentazione al circuito.

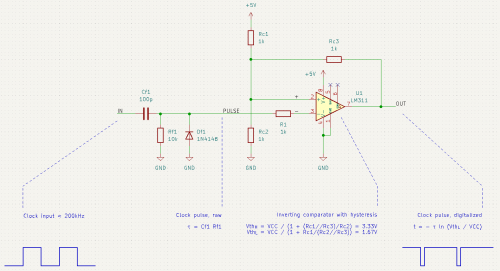

Stuzzica clock

Necessario per adattare l'output del precedente generatore di clock quando si vogliono pilotare CPU con core dinamico. Ripreso dal sito 6502 primer, il circuito è un banale rising edge pulse generator costituito da uno stadio di edge detection seguito da un buffer invertente realizzato con un comparatore.

L'uscita è idle high per poter essere conforme alle specifiche del 6502, che nella sua versione non statica permette di poter prolungare a piacere lo stato alto del clock. Il circuito è tarato per generare impulsi inferiori ai 5μs.

Bus inspector

Step 1 - NOPNOPNOP

- Clock con 555;

- Bus dati bloccato a $EA (NOP);

- Segnali accessori bloccati a default (RDY, IRQB, NMIB, BE, SOB).

Verifica: il bus indirizzi viene incrementato ogni due colpi di clock:

- >=2 colpi di clock con reset;

- 6 colpi di clock per entrare a regime (

7-1)

- A = 0xFFFC

- A = 0xFFFD (lettura vettore reset: 0xEAEA hardcoded)

- A = 0xEAEA

- A = 0xEAEB (legge NOP ed esegue)

- …

Step 2 - ROM + RAM

- Clock con 555;

- una ROM;

- una RAM;

- logica di indirizzamento (74HC00 NAND, eventualmente 74HC04 NOT).

- Dump della memoria ROM

- Disassemblato

Step 3 - Tastiera e display

- Clock con 555;

- una ROM;

- una RAM;

- logica di indirizzamento (74HC00 NAND, 74HC04 NOT, 74HC139 decoder);

- controller tastiera 4×4 (es. 74C922);

- tastiera 4×4;

- display 16×02;

- Schematico

- Sw di esempio

- Wozmon tarocco: versione assolutamente beta del famosissimo monitor per Apple I, riadattata per le risorse del Chippalippa “Step 3”.

Mappa della memoria

L'indirizzamento fatto in questo modo è poco ottimizzato, ma è pratico da fare su una breadboard.

+-------------+ | | 0 + + | | 1 + RAM 32K + | | 2 + + | | 3 +-------------+ | Display | 4 +-------------+ | Keyboard | 5 +-------------+ | | 6 +-------------+ | ROM 8K | 7 +-------------+

* Display R/W command: 0x8000 (in realtà, qualsiasi indirizzo pari nel banco 0x8000-0x9FFF); * Display R/W text: 0x8001 (in realtà, qualsiasi indirizzo dispari nel banco 0x8000-0x9FFF); * Keyboard read: 0xA000 (qualsiasi indirizzo nel banco 0xA000-0xBFFF);

Mappa della memoria (nei sogni)

+-------------+ | | 0 + RAM 16K + | bank switch | 1 +-------------+ |RAM 8K shared| 2 +-------------+ | | 3 +-------------+ | | 4 +-------------+ | | 5 +-------------+ | | 6 +-------------+ | ROM 8K | 7 +-------------+

3-6 Input/Output ( )

)

- VIA

- ACIA

- Display